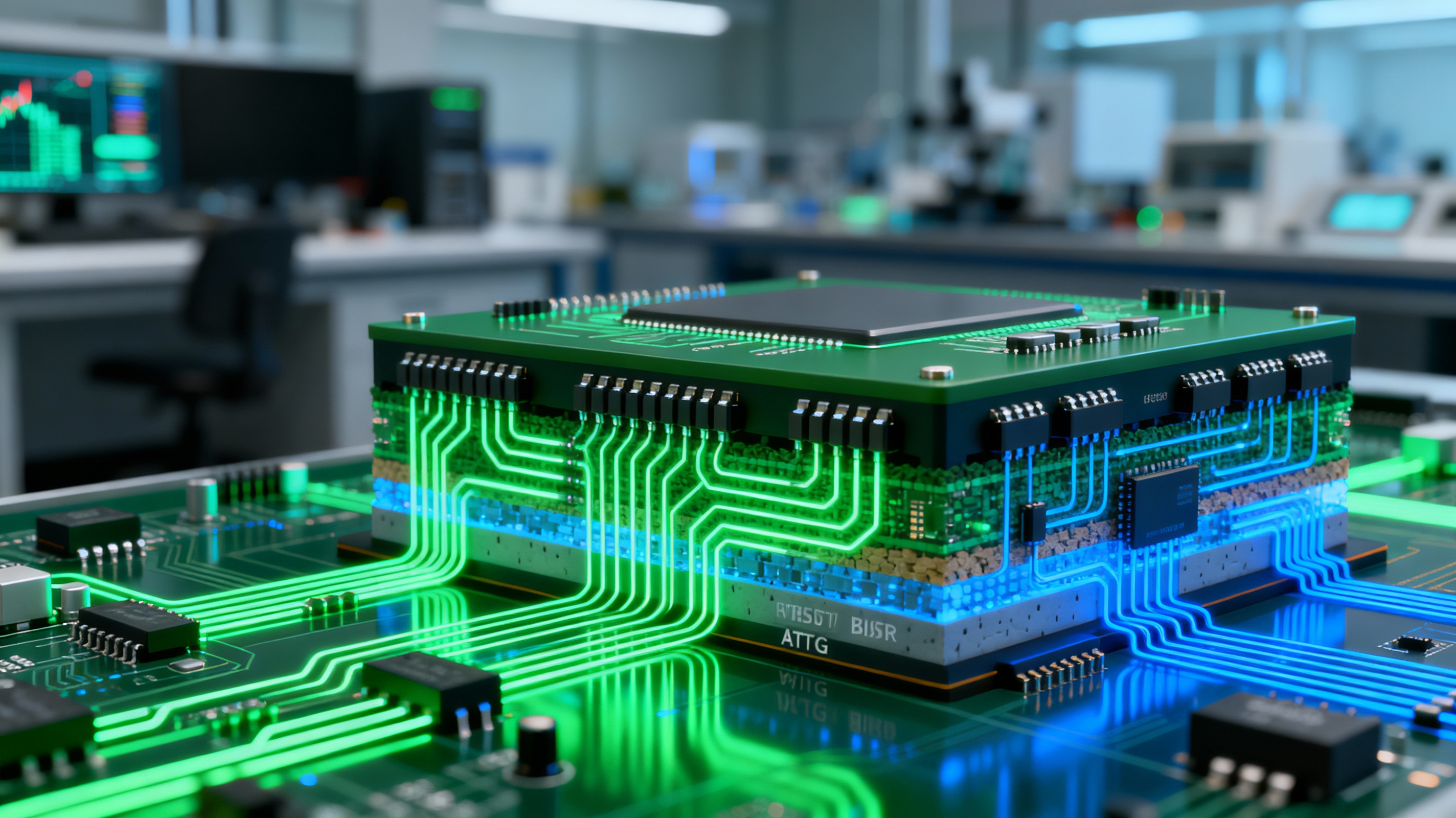

Design for Testability (DFT)

Our DFT (Design for Testability) services ensure high-quality, manufacturable silicon by integrating test structures, scan logic, ATPG patterns, and fault coverage optimization. We support complete DFT implementation from RTL to gate-level validation, ensuring maximum test coverage with minimal area and performance overhead.

Key Capabilities

- 1 Scan insertion (DFT architecture, scan stitching)

- 2 ATPG pattern generation & fault coverage improvement

- 3 Memory BIST (MBIST) insertion & verification

- 4 Logic BIST (LBIST), boundary scan & IEEE 1500

- 5 Scan timing closure, simulations & sign-off checks

Our DFT methodology ensures maximum test coverage, reduced boot-time failures, and simplified production test cycles with industry-standard automation tools.

Why Choose Our DFT Services?

We combine advanced DFT techniques with proven tool expertise to ensure silicon reliability and robust manufacturability across all technology nodes.

High Fault Coverage

Achieving industry-best stuck-at, transition, and path delay fault coverage.

DFT-Compliant Design

Ensuring clean scan chains and optimal test logic with minimal overhead.

Advanced DFT Tools

Expertise in Tessent, Synopsys DFT Compiler, Modus, Tetramax & TestMAX.

Complete DFT Flow

From insertion and ATPG to simulation, sign-off and test pattern readiness.

Our DFT flow covers scan planning, insertion, chain balancing, ATPG, fault simulation, MBIST/LBIST integration, boundary scan, and DFT-aware STA for sign-off-level test readiness.

We use industry-leading DFT tools including Synopsys DFTMAX/DFT Compiler, Cadence Modus, Siemens Tessent (MBIST, Scan, LBIST), and TestMAX ATPG for best test quality and efficiency.

Specializations include hierarchical DFT, low-power DFT, at-speed testing, IEEE 1500 wrappers, MBIST/LBIST architecture, and advanced fault modeling for complex SoC test coverage.